## oreboot on RISC-V Comparing Implementations on Two Platforms Daniel Maslowski

## Agenda

Introduction

Allwinner D1

StarFive JH7100

Approaches and Future Work

## What is oreboot again?

## What is oreboot again?

oreboot is a fork of coreboot...

# OREBOOT

## What is oreboot again?

oreboot is a fork of coreboot...

# OREBOOT

From aa246f71de7f9900a30d938ab618c46839436616 [...]

From: "Ronald G. Minnich" <rminnich@gmail.com>

Date: Mon, 1 Apr 2019 23:48:56 +0000

Subject: [PATCH] Initial removal of C code

https://github.com/oreboot/oreboot

## Firmware in Rust

#### oreboot is a fork of coreboot, with C removed, written in Rust.

Rust logo under CC BY 4.0, https://github.com/rust-lang/rust-artwork Ferris the crab from https://rustacean.net/

feels like an RPG You need to figure out how things work.

feels like an RPG You need to figure out how things work.

point on map = program counter (PC) Sometimes you have no clue where you are.

feels like an RPG You need to figure out how things work.

point on map = program counter (PC) Sometimes you have no clue where you are.

world map = memory map The islands or worlds are the peripherals.

feels like an RPG You need to figure out how things work.

point on map = program counter (PC) Sometimes you have no clue where you are.

world map = memory map The islands or worlds are the peripherals.

player's guide = processor/SoC manual It may be incomplete or not at all available (at least to you).

feels like an RPG You need to figure out how things work.

point on map = program counter (PC) Sometimes you have no clue where you are.

world map = memory map The islands or worlds are the peripherals.

player's guide = processor/SoC manual It may be incomplete or not at all available (at least to you).

Internet of Things = MMORPG Yes, it can get very dangerous.

Many are *marketed* as open source. Are they though?

Many are *marketed* as open source. Are they though?

#### Documentation

schematics and board design manuals and instructions open *license*

Many are *marketed* as open source. Are they though?

#### Documentation

schematics and board design

manuals and instructions

open license

#### Source Code

open tools for flashing, debugging and image composition

firmware, from the start, documented (U-Boot, oreboot, ...)

Linux or other OS, mainline friendly (git fork, not source dump)

all code usable with upstream toolchains, or provide toolchains in a reproducible form (not only binaries for a specific architecture/OS)

Many are *marketed* as open source. Are they though?

#### Documentation

schematics and board design manuals and instructions open *license*

#### Source Code

open tools for flashing, debugging and image composition

firmware, from the start, documented (U-Boot, oreboot, ...)

Linux or other OS, mainline friendly (git fork, not source dump)

all code usable with upstream toolchains, or provide toolchains in a reproducible form (not only binaries for a specific architecture/OS)

OSHWA Certification: https://certification.oshwa.org/

## Let's look at a manual and a memory map!

## Allwinner D1

#### Production widely produced and easily available many different boards from various vendors

Production widely produced and easily available many different boards from various vendors

Cores 1x C906 core, 1GHz https://github.com/T-head-Semi/openc906 1x low-power core, Xtensa HiFi4

Production widely produced and easily available many different boards from various vendors

Cores ↓ 1x C906 core, 1GHz ↓ https://github.com/T-head-Semi/openc906 ↓ 1x low-power core, Xtensa HiFi4

Documentation ↓ larger manual provided ↓ about 1400 pages ↓ DRAM controller and HDMI missing

## D1 Boards and SoMs

#### Allwinner Nezha

first board; Raspberry Pi form factor

#### DongshanPi Nezha STU

SoM in custom form factor

carrier board with many pins

## MangoPi MQ-Pro

#### Sipeed Lichee RV

SoM and multiple carrier boards

# ClockworkPi R01

DevTerm carrier board + case

#### Raspberry Pi Zero form factor, drop-in replacement

https://linux-sunxi.org/Category:D1\_Boards

## D1 Boards: Lichee RV + Dock

## D1 Boards: Lichee RV + Dock

The regular Dock has solder joints for a SPI flash, so I added one.

## D1 Boards: Lichee RV + Dock

The regular Dock has solder joints for a SPI flash, so I added one. The Dock Pro already has a 16 MiB SPI flash, plus a USB serial converter.

#### Mask ROM

Mask ROM

It loads a blob from SPI flash, eMMC or SD card into SRAM (32K).

Mask ROM

It loads a blob from SPI flash, eMMC or SD card into SRAM (32K). The blob has to start with a specific eGON header:

Mask ROM

It loads a blob from SPI flash, eMMC or SD card into SRAM (32K). The blob has to start with a specific eGON header: Disassembly of section .head:

000000000020000 <head\_jump>: 20000: a5 a0 j 0x20068 <start+0x8> 20002: 00 00 unimp

000000000020004 <\_ZN17oreboot\_nezha\_bt09EGON\_HEAD17h5aa4b41b712905f</td>

20004:

65

47

4f

4e

2e

42

54

30

eGON.BT0

2000c:

39

6c

0a

5f

00

00

00

91.\_...

Note:

The header is not documented in the manual.

#### Mask ROM

It loads a blob from SPI flash, eMMC or SD card into SRAM (32K). The blob has to start with a specific eGON header: Disassembly of section .head:

000000000020000 <head\_jump>: 20000: a5 a0 j 0x20068 <start+0x8> 20002: 00 00 unimp

000000000020004 <\_ZN17oreboot\_nezha\_bt09EGON\_HEAD17h5aa4b41b712905f</td>

20004:

65

47

4f

4e

2e

42

54

30

eGON.BT0

2000c:

39

6c

0a

5f

00

00

00

91.\_...

Note:

The header is not documented in the manual.

#### SPI flash

We need to actively read from SPI flash and have no MMIO access to it.

#### SRAM Stage Boot from flash and DRAM init were prototyped separately: https://github.com/luojia65/test-d1-flash-bare/

#### **SRAM Stage**

Boot from flash and DRAM init were prototyped separately: https://github.com/luojia65/test-d1-flash-bare/ It has been copied and developed further in oreboot: src/mainboard/sunxi/nezha/bt0

#### **SRAM Stage**

Boot from flash and DRAM init were prototyped separately: https://github.com/luojia65/test-d1-flash-bare/ It has been copied and developed further in oreboot: src/mainboard/sunxi/nezha/bt0

#### **Payloader Stage**

# D1 oreboot Flow

#### **SRAM Stage**

Boot from flash and DRAM init were prototyped separately: https://github.com/luojia65/test-d1-flash-bare/ It has been copied and developed further in oreboot: src/mainboard/sunxi/nezha/bt0

#### **Payloader Stage**

First RustSBI implementation in oreboot is for Allwinner Nezha (D1): src/mainboard/sunxi/nezha/main

Remember: The DRAM controller is not documented in the manual, only its existence.

Remember: The DRAM controller is not documented in the manual, only its existence.

a bit less than 2000 lines of code

translated from C, which was translated from assembly dump

Remember: The DRAM controller is not documented in the manual, only its existence.

- 🔋 a bit less than 2000 lines of code

- translated from C, which was translated from assembly dump

There are configurations per board. They could technically be determined at runtime.

Remember: The DRAM controller is not documented in the manual, only its existence.

- 🔋 a bit less than 2000 lines of code

- translated from C, which was translated from assembly dump

There are configurations per board. They could technically be determined at runtime.

community has knowledge on how it works

some documentation on https://linux-sunxi.org

Remember: The DRAM controller is not documented in the manual, only its existence.

- 🔋 a bit less than 2000 lines of code

- translated from C, which was translated from assembly dump

There are configurations per board. They could technically be determined at runtime.

community has knowledge on how it works some documentation on https://linux-sunxi.org

I tried my best to name registers; reviews and help wanted!

We may be able to reuse at least parts, and apply them to other Allwinner SoCs.

avilable in main branch boot from SPI flash SD card work in progress SBI is optional multiple boards supported

avilable in main branch boot from SPI flash SD card work in progress SBI is optional multiple boards supported 3 We can boot Linux \o/ xv6 MnemOS r9 more to come: FreeBSD, Illumos...

avilable in main branch boot from SPI flash SD card work in progress SBI is optional multiple boards supported We can boot Linux \o/ xv6 MnemOS r9 more to come: FreeBSD, Illumos... Bare metal testing app

https://github.com/adamgreig/d1rgb

# StarFive JH7100

#### Production

no longer produced, *but* the successor JH7110 SoC appears to be using the same DRAM controller and parts, judging from very similar vendor code

#### Production

no longer produced, *but* the successor JH7110 SoC appears to be using the same DRAM controller and parts, judging from very similar vendor code

Cores 2x U74 core, >1GHz https://sifive.cdn.prismic.io/sifive/ad5577a0-9a00-45c9-a5d0-424a3d586060\_u74\_core\_complex\_manual\_21G3.pdf 1x VP6

#### Production

no longer produced, *but* the successor JH7110 SoC appears to be using the same DRAM controller and parts, judging from very similar vendor code

Cores 2x U74 core, >1GHz ► https://sifive.cdn.prismic.io/sifive/ad5577a0-9a00-45c9-a5d0-424a3d586060\_u74\_core\_complex\_manual\_21G3.pdf Tx VP6

## Documentation

no full manual publicly available

instructions for firmware recovery with open tools

sparse datasheet with list of peripheral blocks and suppliers (p23)

less than 140 pages https://github.com/starfive-tech/JH7100 docs

# JH7100 Boards

# JH7100 Boards

BeagleV

only a select few people received the board as a prototype

# JH7100 Boards

#### **BeagleV**

only a select few people received the board as a prototype

obtained via RISC-V International developer program https://riscv.org/risc-v-developer-boards/details/

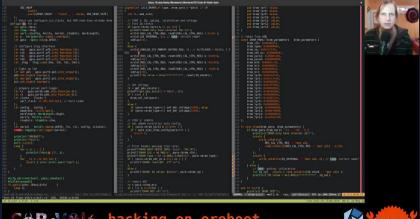

# JH7100 Development Stream

#### Live: https://twitch.tv/cyrevolt

## CRANT hacking on oreboot

Archive: https://www.youtube.com/playlist?list=PLenOHeTI A9PSGshD nEc4dYK-GSnCshk6

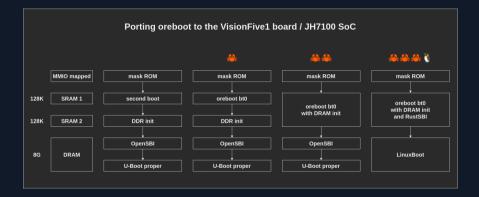

# JH7100 Vendor Code and Transition Plan

M

Mask ROM not documented; can be dumped via preflashed U-Boot

#### Mask ROM

not documented; can be dumped via preflashed U-Boot It loads a blob to SRAM, which has to be prefixed with a 4-byte value for its size.

#### Mask ROM

not documented; can be dumped via preflashed U-Boot It loads a blob to SRAM, which has to be prefixed with a 4-byte value for its size.

SPI flash

#### Mask ROM

not documented; can be dumped via preflashed U-Boot It loads a blob to SRAM, which has to be prefixed with a 4-byte value for its size.

## SPI flash

MMIO access to the SPI flash is available, requiring little initialization.

#### Mask ROM

not documented; can be dumped via preflashed U-Boot It loads a blob to SRAM, which has to be prefixed with a 4-byte value for its size.

## SPI flash

MMIO access to the SPI flash is available, requiring little initialization. This means that loading from flash is just like copying from on area in memory to another.

#### Mask ROM

not documented; can be dumped via preflashed U-Boot It loads a blob to SRAM, which has to be prefixed with a 4-byte value for its size.

### SPI flash

MMIO access to the SPI flash is available, requiring little initialization. This means that loading from flash is just like copying from on area in memory to another.

#### **Multicore**

Note: Multiple cores allows for accessing peripherals in parallel.

#### Mask ROM

not documented; can be dumped via preflashed U-Boot It loads a blob to SRAM, which has to be prefixed with a 4-byte value for its size.

### SPI flash

MMIO access to the SPI flash is available, requiring little initialization. This means that loading from flash is just like copying from on area in memory to another.

#### Multicore

Note: Multiple cores allows for accessing peripherals in parallel. Strategy: loop second hart; when done with peripherals, jump to OS.

We started with a case study, analyzing how the vendor code works. https://github.com/starfive-tech/JH7100\_ddrinit

We started with a case study, analyzing how the vendor code works.

https://github.com/starfive-tech/JH7100\_ddrinit

more than 4000 lines

quite some registers have comments

lots of magic values, little logic

more than 50% is just writing 0, probably unnecessary

We started with a case study, analyzing how the vendor code works.

https://github.com/starfive-tech/JH7100\_ddrinit

more than 4000 lines

quite some registers have comments

lots of magic values, little logic

more than 50% is just writing 0, probably unnecessary

We found and fixed a double bug in the vendor code:

writing back to the wrong register

We started with a case study, analyzing how the vendor code works.

https://github.com/starfive-tech/JH7100\_ddrinit

more than 4000 lines

quite some registers have comments

lots of magic values, little logic

more than 50% is just writing 0, probably unnecessary

We found and fixed a double bug in the vendor code:

writing back to the wrong register

We reported the issue, with no reply so far.

https://github.com/starfive-tech/JH7100\_ddrinit/issues/14

# JH7100 Development Status

oreboot 🖀 Read from SRAMO BASE 0x1800 0000: 37f441293e2042320df193e1042320df193e4042320df1b54e2320 Read from SPI FLASH BASE 0x2001 0000: f055109712009382c29673905230735003073504030f32240f1b221781 RISC-V vendor 489 arch 8000000000000007 imp 20190531 DRAM init DRAM clocks done DRAM PHYO init DRAM PHY0 PI DRAM PHY0 start DRAM PHYO clock DRAM PHY0 done DRAM PHV1 done DRAM test DDR @00100000. 1M test done DDR @00200000. 2M test done GOTO MATN

pull request open with DRAM init and jump to next stage https://github.com/oreboot/oreboot/pull/606

we currently load and jump to the U-Boot + OpenSBI blob

which can then load Linux, e.g., via network

# Approaches and Future Work

**Register Blocks**

#### **Register Blocks**

A register block is a set of register that maps to a block in the SoC.

#### **Register Blocks**

A register block is a set of register that maps to a block in the SoC. The start is called the *base register*.

#### **Register Blocks**

A register block is a set of register that maps to a block in the SoC. The start is called the *base register*. const CCU\_BASE: usize = 0x0200\_1000; const CCU\_PLL\_PERIO\_CTRL: usize = CCU\_BASE + 0x0020;

$\bigwedge$

#### **Register Blocks**

A register block is a set of register that maps to a block in the SoC. The start is called the *base register*. const CCU\_BASE: usize = 0x0200\_1000; const CCU\_PLL\_PERIO\_CTRL: usize = CCU\_BASE + 0x0020;

## MMIO (memory-mapped input/output)

Writing to a peripheral register happens through a memory write instruction.

#### **Register Blocks**

A register block is a set of register that maps to a block in the SoC. The start is called the *base register*. const CCU\_BASE: usize = 0x0200\_1000; const CCU\_PLL\_PERIO\_CTRL: usize = CCU\_BASE + 0x0020;

## MMIO (memory-mapped input/output)

Writing to a peripheral register happens through a memory write instruction.

To change a value, read first, apply a mask, and write back.

#### **Register Blocks**

A register block is a set of register that maps to a block in the SoC. The start is called the *base register*. const CCU\_BASE: usize = 0x0200\_1000; const CCU\_PLL\_PERIO\_CTRL: usize = CCU\_BASE + 0x0020;

## MMIO (memory-mapped input/output)

Writing to a peripheral register happens through a memory write instruction.

To change a value, read first, apply a mask, and write back. Example:

unsafe {

let peri0\_ctrl = read\_volatile(CCU\_PLL\_PERI0\_CTRL as \*mut u32); let new\_val = peri0\_ctrl | 1 << 29; // set bit `29` write\_volatile(CCU\_PLL\_PERI0\_CTRL as \*mut u32, new\_val);

https://github.com/duskmoon314/aw-pac/tree/main/d1-pac

https://github.com/duskmoon314/aw-pac/tree/main/d1-pac https://docs.rs/d1-pac/latest/d1\_pac

#### https://github.com/duskmoon314/aw-pac/tree/main/d1-pac

https://docs.rs/d1-pac/latest/d1\_pac

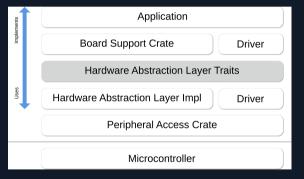

Image under CC BY 4.0

#### https://github.com/duskmoon314/aw-pac/tree/main/d1-pac

https://docs.rs/d1-pac/latest/d1\_pac

| Uses Implements |  | Application                            |  |

|-----------------|--|----------------------------------------|--|

|                 |  | Board Support Crate Driver             |  |

|                 |  | Hardware Abstraction Layer Traits      |  |

|                 |  | Hardware Abstraction Layer Impl Driver |  |

|                 |  | Peripheral Access Crate                |  |

|                 |  | Microcontroller                        |  |

## Image under CC BY 4.0 Layers in oreboot 1. App (mainboard)

- 2. HAL ("drivers")

- 3. PAC (if available)

#### https://github.com/duskmoon314/aw-pac/tree/main/d1-pac

https://docs.rs/d1-pac/latest/d1\_pac

# Instead of using write\_volatile directly, we call a *semantic function* from a library:

# Instead of using write\_volatile directly, we call a *semantic function* from a library:

// light up led let mut pb5 = gpio.portb.pb5.into\_output(); pb5.set\_high().unwrap();

# Instead of using write\_volatile directly, we call a *semantic function* from a library:

// light up led let mut pb5 = gpio.portb.pb5.into\_output(); pb5.set\_high().unwrap();

Depending on the API, we may need to use a writer interface and pass a function:

# Instead of using write\_volatile directly, we call a *semantic function* from a library:

// light up led let mut pb5 = gpio.portb.pb5.into\_output(); pb5.set\_high().unwrap();

Depending on the API, we may need to use a writer interface and pass a function:

ccu.smhc0\_clk.write(|w| w.clk\_src\_sel().pll\_peri\_1x());

*Runtime Services* are listed in **platform specs**, referencing the **SBI spec**. https://github.com/riscv/riscv-platform-specs

*Runtime Services* are listed in **platform specs**, referencing the **SBI spec**. https://github.com/riscv/riscv-platform-specs

The SBI (*Supervisor Binary Interface*) spec is a living document: https://github.com/riscv-non-isa/riscv-sbi-doc

*Runtime Services* are listed in **platform specs**, referencing the **SBI spec**. https://github.com/riscv/riscv-platform-specs

The SBI (*Supervisor Binary Interface*) spec is a living document: https://github.com/riscv-non-isa/riscv-sbi-doc

It defines extensions and functions similar to system calls.

*Runtime Services* are listed in **platform specs**, referencing the **SBI spec**. https://github.com/riscv/riscv-platform-specs

The SBI (*Supervisor Binary Interface*) spec is a living document: https://github.com/riscv-non-isa/riscv-sbi-doc

It defines extensions and functions similar to system calls.

Ports need to be written per platform (core/SoC/board). We have one for the D1.

*Runtime Services* are listed in **platform specs**, referencing the **SBI spec**. https://github.com/riscv/riscv-platform-specs

The SBI (*Supervisor Binary Interface*) spec is a living document: https://github.com/riscv-non-isa/riscv-sbi-doc

It defines extensions and functions similar to system calls.

Ports need to be written per platform (core/SoC/board). We have one for the D1.

In oreboot, we use RustSBI. https://github.com/rustsbi/rustsbi https://docs.rs/rustsbi/latest/rustsbi/

# The platform specs define sets of instructions necessary in order to run an OS.

The platform specs define sets of instructions necessary in order to run an OS.

There are *Control and Status Registers (CSRs)*, similar to x86 MSRs.

The platform specs define sets of instructions necessary in order to run an OS.

There are Control and Status Registers (CSRs), similar to x86 MSRs.

They allow for vendor specific custom extensions.

The platform specs define sets of instructions necessary in order to run an OS.

There are Control and Status Registers (CSRs), similar to x86 MSRs.

They allow for vendor specific custom extensions.

They may be required for full usage of the SoC.

The platform specs define sets of instructions necessary in order to run an OS.

There are *Control and Status Registers (CSRs)*, similar to x86 MSRs. They allow for vendor specific custom extensions. They *may* be required for full usage of the SoC. Vendors may also implement custom instructions.

The platform specs define sets of instructions necessary in order to run an OS.

There are Control and Status Registers (CSRs), similar to x86 MSRs.

They allow for vendor specific custom extensions.

They may be required for full usage of the SoC.

Vendors may also implement custom instructions.

Both CSRs and custom instructions may be neglected, and a subset of the SoC's capabilities be used.

BL808

already available (I have multiple boards)

1x C906 (512MHz), 1x E907, 1x low-power core

**BL808**

already available (I have multiple boards) 1x C906 (512MHz), 1x E907, 1x low-power core

JH7110 already available; some people received theirs from crowdfunding campaign marketed as open source no manual available initial U-Boot and Linux sources available https://github.com/starfivetech/Tools is closed source

BL808

already available (I have multiple boards) 1x C906 (512MHz), 1x E907, 1x low-power core

### JH7110

already available; some people received theirs from crowdfunding campaign *marketed* as *open* source

no manual available

initial U-Boot and Linux sources available

https://github.com/starfive-tech/Tools is closed source

#### TH1520

SoM with SPI flash placeholder coming soon multiple boards offered https://sipeed.com/licheepi4a Lichee Pi 4A Lichee Cluster 4A Lichee Router 4A Lichee Pad/Phone 4A

#### layoutflash

library within oreboot

idea: DTS for flash partitioning

other ideas: add SBoM

#### layoutflash

library within oreboot

idea: DTS for flash partitioning

other ideas: add SBoM

#### xtask

Rust build framework used in oreboot needs extension with more boards and common functions factored out

#### layoutflash

library within oreboot

idea: DTS for flash partitioning

other ideas: add SBoM

#### xtask

Rust build framework used in oreboot needs extension with more boards and common functions factored out

#### ARM and other ISAs

We had some ARM and x86 boards and discarded them in favor of getting on.

However, there are issues tracking their status with starting points. https://github.com/oreboot/oreboot/issues

## Follow Me

https://github.com/orangecms https://twitter.com/orangecms https://twitch.tv/cyrevolt https://youtube.com/@cyrevolt

Daniel Maslowski

https://github.com/oreboot/oreboot

https://metaspora.org/oreboot-comparison-riscv-d1-jh7100.pdf